Diferite tipuri de sisteme digitale sunt construite din foarte puține tipuri de configurații de rețea de bază, cum ar fi poarta ȘI, poarta NAND, Poarta sau etc ... Aceste circuite elementare sunt utilizate de nenumărate ori în diferite combinații topologice. Pe lângă efectuarea logicii, sistemele digitale trebuie să stocheze și numere binare. Pentru aceste celule de memorie, cunoscute și sub numele de ȘLAP' sunt proiectate. Pentru a efectua unele funcții, cum ar fi adăugarea binară. Prin urmare, pentru a îndeplini astfel de funcții, combinații de porți logice și FLIP-FLOP sunt proiectate pe un IC cu un singur cip. Aceste IC formează elementele practice ale sistemelor digitale. Unul dintre astfel de elemente utilizate pentru adăugarea binară este Adăugătorul Carry Look-ahead.

Ce este un Adder Carry Look-forward?

Un computer digital trebuie să conțină circuite care pot efectua operații aritmetice, cum ar fi adunarea, scăderea, multiplicarea și divizarea. Dintre acestea, adunarea și scăderea sunt operațiile de bază, în timp ce înmulțirea și împărțirea sunt adunarea și respectiv scăderea repetate.

Pentru a efectua aceste operațiuni, „circuitele Adder” sunt implementate folosind porți logice de bază. Circuite sumatoare sunt evoluate ca Adder Half-Adder, Full-Adder, Ripple-carry Adder și Carry Look-ahead Adder.

Printre acestea, Carry Look-ahead Adder este circuitul mai rapid al sumatorului. Reduce întârzierea de propagare, care are loc în timpul adăugării, prin utilizarea unor circuite hardware mai complexe. Este proiectat prin transformarea circuitului Adder-ripple-carry astfel încât logica de transport a sumatorului să fie schimbată în logică pe două niveluri.

Sumator 4-Bit Carry Look-forward

În sumatoare paralele, ieșirea de transport a fiecărei sumatoare complete este dată ca intrare de transfer la următoarea stare de ordin superior. Prin urmare, aceste adăugătoare nu este posibil să producă ieșiri de transfer și sumă ale oricărei stări, cu excepția cazului în care este disponibilă o intrare de transfer pentru acea stare.

Deci, pentru ca calculul să aibă loc, circuitul trebuie să aștepte până când bitul de transport se propagă în toate stările. Acest lucru induce întârzierea propagării transportului în circuit.

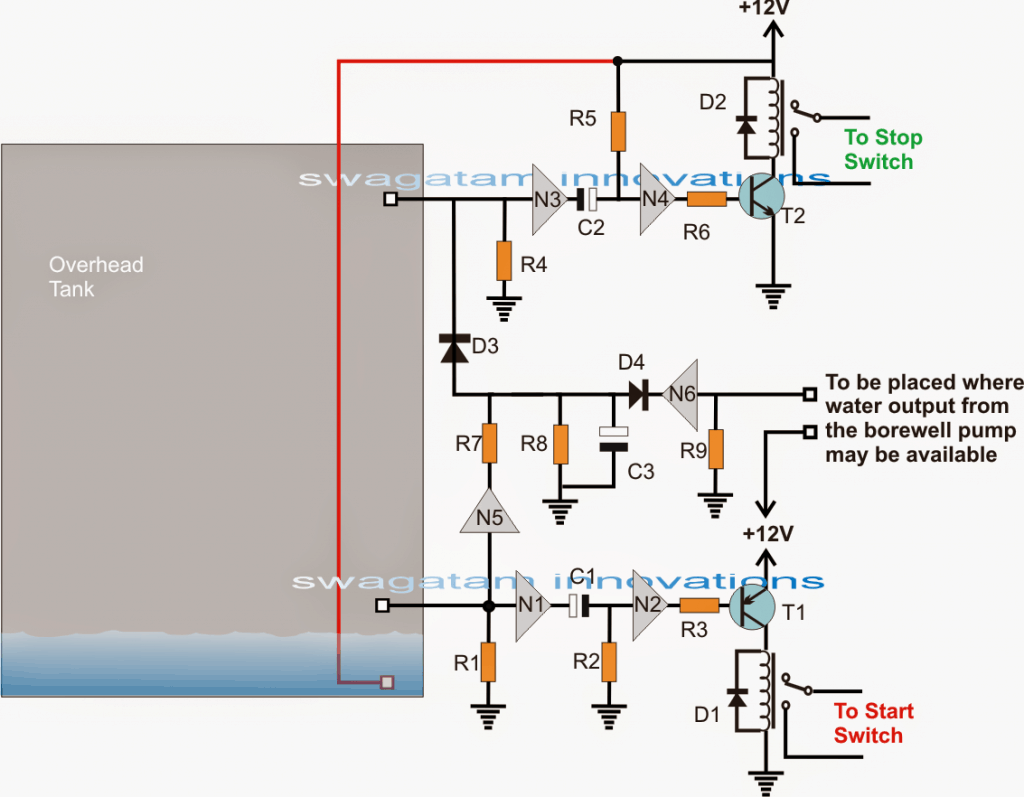

4-bit-Ripple-Carry-Adder

Luați în considerare circuitul de adăugare a purtătorului de 4 biți de mai sus. Aici suma S3 poate fi produsă de îndată ce sunt date intrările A3 și B3. Dar carry C3 nu poate fi calculat până când bitul de carry C2 nu este aplicat, în timp ce C2 depinde de C1. Prin urmare, pentru a produce rezultate finale la starea de echilibru, transportul trebuie să se propage prin toate stările. Acest lucru mărește întârzierea de propagare a circuitului.

Întârzierea de propagare a sumatorului este calculată ca „întârzierea de propagare a fiecărei porți de ori numărul de etape din circuit”. Pentru calcularea unui număr mare de biți, trebuie adăugate mai multe etape, ceea ce face ca întârzierea să fie mult mai gravă. Prin urmare, pentru a rezolva această situație, a fost introdus Cadd Look-ahead Adder.

Pentru a înțelege funcționarea unui Cadd Look-forward Adder, este descris mai jos un Caddder Carry Look-forward de 4 biți.

4-bit-Carry-Look-ahead-Adder-Logic-Diagram

În acest sumator, intrarea de transport în orice etapă a sumatorului este independentă de biții de transport generați în etapele independente. Aici ieșirea oricărei etape depinde doar de biții care sunt adăugați în etapele anterioare și de intrarea de transport furnizată la etapa inițială. Prin urmare, circuitul din orice etapă nu trebuie să aștepte generarea de carry-bit din etapa anterioară și bitul de transport poate fi evaluat în orice moment al timpului.

Tabelul Adevărului al Adderului Carry Look-forward

Pentru derivarea tabelului de adevăr al acestui sumator, sunt introduși doi termeni noi - Generare și propagare. Carry generate Gi = 1 ori de câte ori este generat un carry Ci + 1. Depinde de intrările Ai și Bi. Gi este 1 când Ai și Bi sunt 1. Prin urmare, Gi este calculat ca Gi = Ai. Bi.

Carry propagat Pi este asociat cu propagarea transportului de la Ci la Ci + 1. Se calculează ca Pi = Ai ⊕ Bi. Tabelul de adevăr al acestui sumator poate fi derivat din modificarea tabelului de adevăr al unui sumator complet.

Folosind termenii Gi și Pi, Suma Si și Carry Ci + 1 sunt prezentate mai jos -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Prin urmare, biții de transport C1, C2, C3 și C4 pot fi calculați ca

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Se poate observa din ecuațiile care transportă Ci + 1 depinde doar de transportul C0, nu de biții de transport intermediari.

Carry-Look-ahead-Adder-Truth-Table

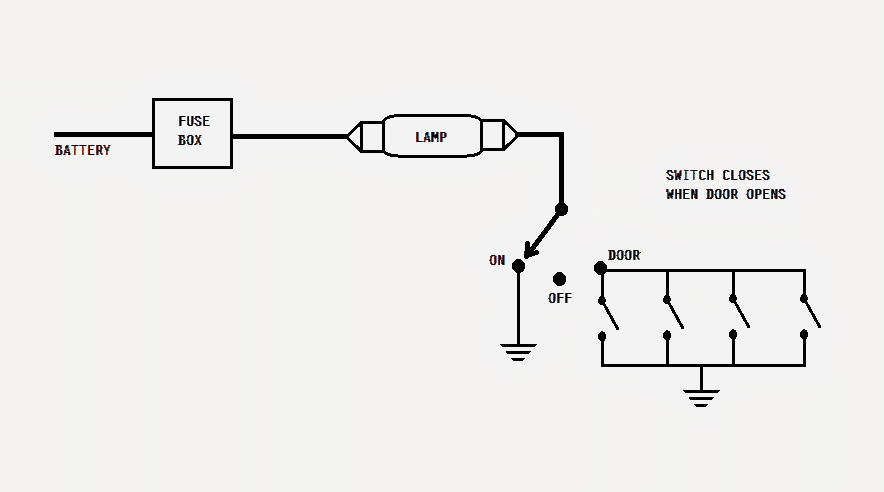

Diagrama circuitului

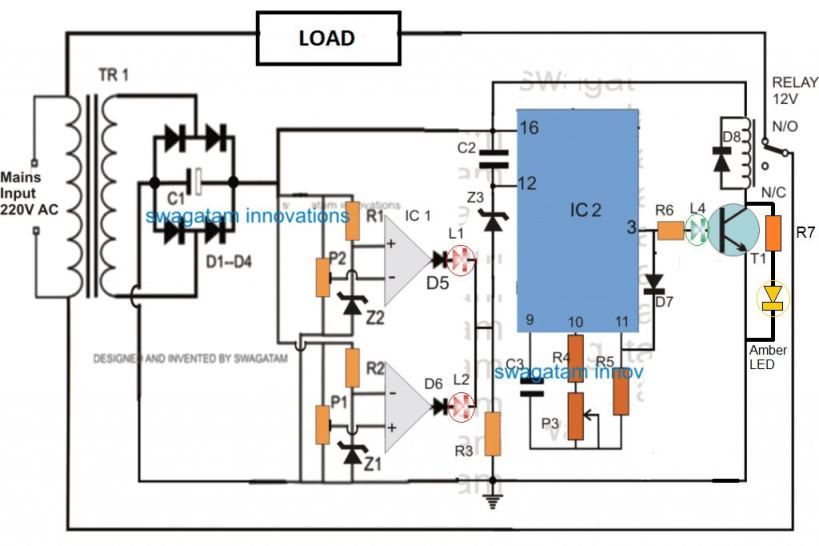

Ecuațiile de mai sus sunt implementate folosind circuite combinaționale pe două niveluri împreună cu porțile AND, OR, unde porțile sunt presupuse a avea intrări multiple.

Carry-Output-Generation-Circuit-of-Carry-Look-forward-Adder

Circuitul Carry Look-ahead Adder pentru 4 biți este prezentat mai jos.

Diagrama circuitului 4-bit-Carry-Look-forward-Adder

Circuitele Adder de 8-bit și 16-bit Carry Look-forward Adder pot fi proiectate prin cascada circuitului sumator de 4 biți cu logică de transport.

Avantajele Carry Look-ahead Adder

În acest sumator, întârzierea propagării este redusă. Ieșirea de transport în orice etapă depinde doar de bitul de transport inițial al etapei de început. Folosind acest sumator este posibil să se calculeze rezultatele intermediare. Acest sumator este cel mai rapid sumator utilizat pentru calcul.

Aplicații

Aditivii Carry Look-forward de mare viteză sunt utilizați ca implementați ca IC-uri. Prin urmare, este ușor să încorporați sumatorul în circuite. Prin combinarea a două sau mai multe addere se pot face cu ușurință calcule ale funcțiilor booleene de biți mai mari. Aici creșterea numărului de porți este, de asemenea, moderată atunci când este utilizată pentru biți mai mari.

Pentru acest Adder există un compromis între zonă și viteză. Atunci când este utilizat pentru calcule de biți mai mari, oferă viteză mare, dar complexitatea circuitului este, de asemenea, crescută, crescând astfel zona ocupată de circuit. Acest sumator este de obicei implementat ca module pe 4 biți care sunt în cascadă împreună atunci când sunt utilizate pentru calcule mai mari. Această sumă este mai costisitoare în comparație cu alte mașini de adăugat.

Pentru calculul boolean în computere, adăugatoarele sunt utilizate în mod regulat. Charles Babbage a implementat un mecanism de anticipare a bitului de transport în computere, pentru a reduce întârzierea cauzată de aditivi pentru transportarea ondulatiei . În timpul proiectării unui sistem, viteza de calcul este cel mai mare factor decisiv pentru un proiectant. În 1957, Gerald B. Rosenberger a brevetat modernul Binary Carry Look-ahead Adder. Pe baza analizei întârzierii și simularii porții, se efectuează experimente pentru a modifica circuitul acestui sumator pentru a-l face și mai rapid. Pentru un sumator de n-bit carry-forward, care este întârzierea de propagare, când o întârziere a fiecărei porți este de 20?

Credit de imagine