Pentru executarea unui program de computer, acesta necesită funcționarea sincronă a mai multor componente ale unui computer. De exemplu, Procesoare - furnizarea informațiilor de control necesare, adrese ... etc, autobuze - pentru a transfera informații și date către și din memorie către dispozitive I / O ... etc. Factorul interesant al sistemului ar fi modul în care gestionează transferul de informații între procesor, memorie și dispozitive I / O. De obicei, procesoarele controlează tot procesul de transfer de date, chiar de la inițierea transferului la stocarea datelor la destinație. Acest lucru adaugă încărcarea procesorului și de cele mai multe ori acesta rămâne în starea ideală, scăzând astfel eficiența sistemului. Pentru a accelera transferul de date între dispozitivele I / O și memorie, controlerul DMA acționează ca master master. Controlerul DMA transferă date cu o intervenție minimă a procesorului.

Ce este un controler DMA?

Termenul DMA înseamnă acces direct la memorie. Dispozitivul hardware utilizat pentru accesul direct la memorie se numește controler DMA. DMA controlerul este o unitate de control , parte a dispozitivului I / O circuit de interfață , care poate transfera blocuri de date între dispozitivele I / O și memoria principală cu o intervenție minimă de la procesor.

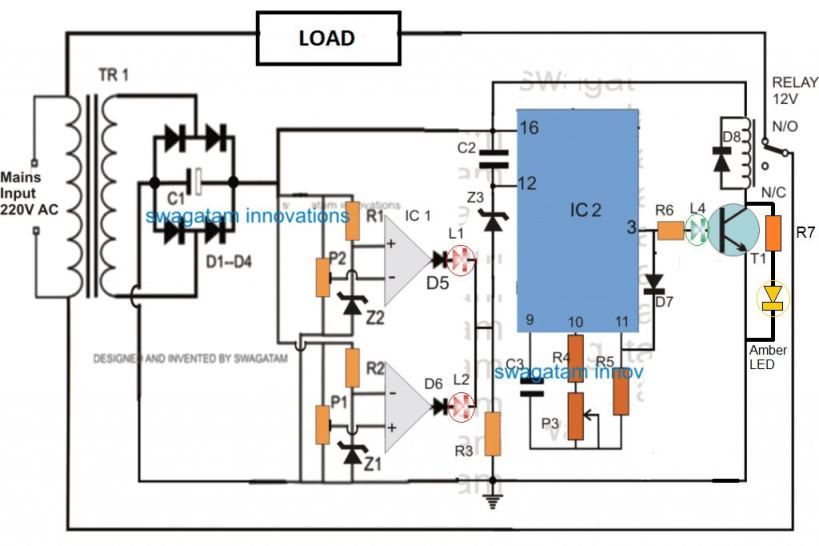

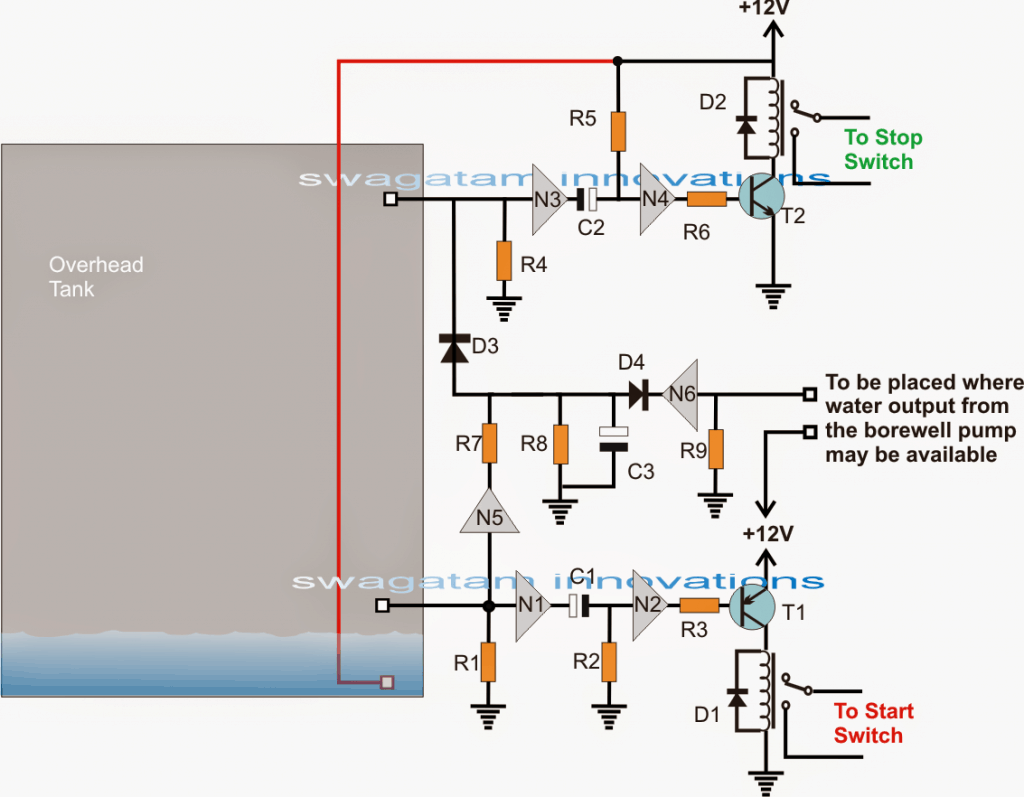

Diagrama controlerului DMA în arhitectura computerelor

Controlerul DMA oferă o interfață între magistrală și dispozitivele de intrare-ieșire. Deși transferă date fără intervenția procesorului, este controlat de procesor. Procesorul inițiază controlerul DMA trimițând adresa de pornire, numărul de cuvinte din blocul de date și direcția de transfer a datelor. de la dispozitive I / O la memorie sau din memoria principală la dispozitive I / O. La controlerul DMA pot fi conectate mai multe dispozitive externe.

DMA în arhitectura computerelor

Controlerul DMA conține o unitate de adrese, pentru generarea de adrese și selectarea dispozitivului I / O pentru transfer. De asemenea, conține unitatea de control și numărul de date pentru păstrarea numărului de blocuri transferate și indicarea direcției de transfer a datelor. Când transferul este finalizat, DMA informează procesorul ridicând o întrerupere. Diagrama bloc tipică a controlerului DMA este prezentată în figura de mai jos.

Diagrama bloc tipică a controlerului DMA

Funcționarea controlerului DMA

Controlerul DMA trebuie să împartă magistrala cu procesorul pentru a efectua transferul de date. Dispozitivul care ține autobuzul la un moment dat se numește magistral de autobuz. Când trebuie efectuat un transfer de la dispozitivul I / O către memorie sau viceversa, procesorul oprește executarea programului curent, cu pași programul contor, mută datele peste stivă, apoi trimite un semnal de selectare DMA către controlerul DMA prin magistrala de adrese.

Dacă controlerul DMA este liber, solicită controlul magistralei de la procesor ridicând semnalul de solicitare a magistralei. Procesorul acordă magistrala către controler ridicând semnalul de acordare a magistralei, acum controlerul DMA este maestrul magistralei. Procesorul inițiază controlerul DMA trimițând adresele de memorie, numărul de blocuri de date care urmează să fie transferate și direcția de transfer a datelor. După alocarea sarcinii de transfer de date controlerului DMA, în loc să aștepte în mod ideal până la finalizarea transferului de date, procesorul reia executarea programului după preluarea instrucțiunilor din stivă.

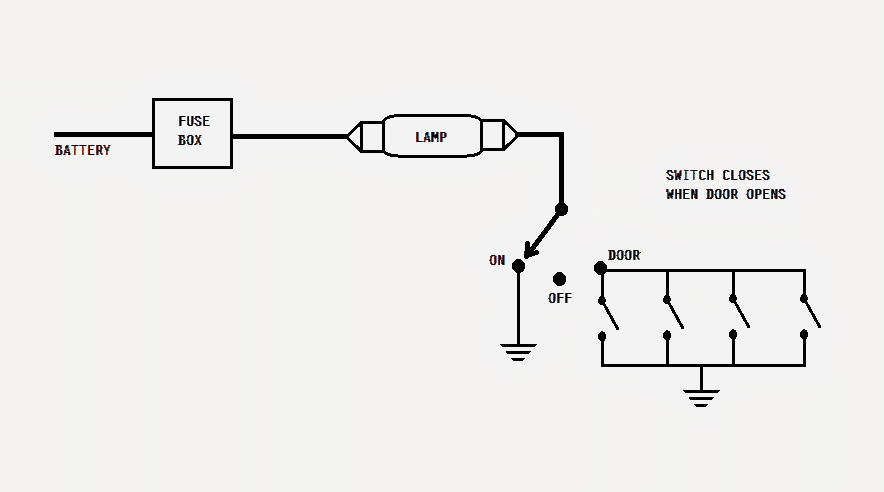

Transferul datelor în computer de către controlerul DMA

Controlerul DMA are acum controlul complet al autobuzelor și poate interacționa direct cu dispozitivele de memorie și I / O, indiferent de CPU. Realizează transferul de date conform instrucțiunilor de control primite de procesor. După finalizarea transferului de date, acesta dezactivează semnalul de solicitare a magistralei, iar CPU dezactivează semnalul de acordare a magistralei, mutând astfel controlul autobuzelor către CPU.

Când un dispozitiv I / O dorește să inițieze transferul, acesta trimite un semnal de cerere DMA către controlerul DMA, pentru care controlerul recunoaște dacă este gratuit. Apoi controlerul solicită procesorului autobuzul, ridicând semnalul de solicitare a autobuzului. După primirea semnalului de acordare a autobuzului, acesta transferă datele de pe dispozitiv. Pentru n controler DMA canalizat, se pot conecta un număr de dispozitive externe.

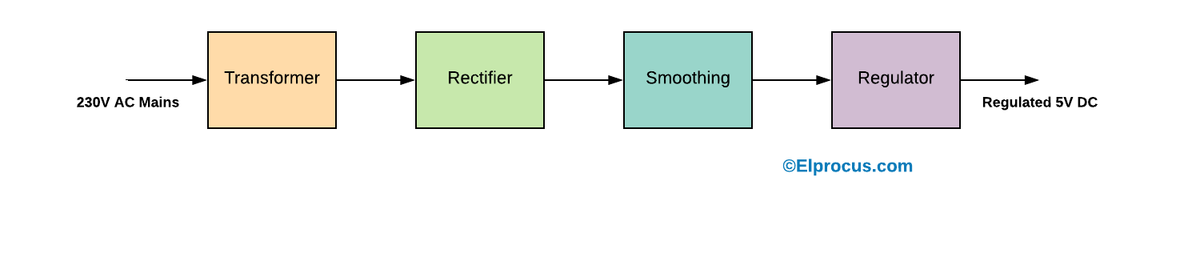

DMA transferă datele în trei moduri, care includ următoarele.

la) Foc continuu : În acest mod, DMA predă autobuzele către CPU numai după finalizarea întregului transfer de date. Între timp, dacă CPU necesită autobuzul, acesta trebuie să rămână ideal și să aștepte transferul de date.

b) Modul furt furt : În acest mod, DMA oferă controlul autobuzelor către CPU după transferul fiecărui octet. Emite continuu o cerere pentru controlul autobuzului, efectuează transferul unui octet și returnează autobuzul. Prin acest procesor nu trebuie să aștepte mult timp dacă are nevoie de un autobuz pentru sarcini cu prioritate mai mare.

c) Mod transparent: Aici, DMA transferă date numai atunci când CPU execută instrucțiunile care nu necesită utilizarea autobuzelor.

8237 Controler DMA

- 8237 are 4 canale I / O împreună cu flexibilitatea de a crește numărul de canale.

- Fiecare canal poate fi programat individual și are o adresă de 64k și capacitate de date.

- Blocul de control al sincronizării, blocul de comandă al programului, blocul de codificare prioritară sunt cele trei blocuri principale ale 8237A.

- Semnalizarea internă și controlul extern sunt conduse de blocul de control al temporizării.

- Diverse comenzi date de microprocesor către DMA sunt decodate de blocul de control al comenzilor programului.

- Ce canal trebuie să aibă cea mai mare prioritate este decis de prioritate bloc codificator .

8237A are 27 de registre interne.

8237A funcționează în două cicluri - ciclu ideal și ciclu activ, unde fiecare ciclu conține 7 stări separate compuse din câte o perioadă de ceas fiecare.

S0- Prima stare, în care controlerul a solicitat autobuzul și așteaptă confirmarea de la procesor.

S1, S2, S3, S4 se numesc stările de lucru ale 8237A unde are loc transferul efectiv de date. Dacă este nevoie de mai mult timp pentru transferul stărilor de așteptare, se adaugă SW între aceste stări.

Pentru transferul de memorie în memorie trebuie efectuate transferuri de citire din memorie și de scriere în memorie. Pentru un singur transfer sunt necesare opt stări. Primele patru stări cu indicele S11, S12, S13, S14 efectuează transferul de citire din memorie și următoarele patru S21, S22, S23, S24 sunt pentru transferul de scriere în memorie.

DMA intră în starea ideală atunci când niciun canal nu solicită servicii și efectuează starea SI. SI este o stare inactivă în care DMA este inactiv până când primește o cerere. În această stare, DMA se află în condiții de program în care procesorul poate programa DMA.

Când DMA se află în starea ideală și nu mai primește alte cereri de canal, acesta transmite un semnal HRQ către procesor și intră în stare activă, unde poate începe transferul de date fie prin modul rafală, modul furt furt ciclu sau modul transparent.

8237 Diagrama pinilor

8257 Controler DMA

Atunci când este asociat cu un singur port Intel 8212 I / O, controlerul 8257 DMA formează un canal complet cu 4 canale Controler DMA . La primirea unei cereri de transfer, controlerul 8257-

- Obține controlul asupra magistralei de sistem de la procesor.

- Se recunoaște perifericul conectat la canalul cu cea mai mare prioritate.

- Biții cel mai puțin semnificativi ai adresei de memorie sunt mutați peste liniile de adresă A0-A7 ale magistralei de sistem.

- Cea mai semnificativă 8 biți ale adresei de memorie sunt conduse la portul I / O 8212 prin linii de date.

- Generează semnalele de control adecvate pentru transferul de date între periferice și locațiile de memorie adresate.

- Când se transferă numărul specificat de octeți, controlerul informează sfârșitul procesului de transfer prin activarea ieșirii numărului de terminale (TC).

Pentru fiecare canal 8257 conține două Registre pe 16 biți - 1) Registrul de adrese DMA și 2) Registrul de numărare a terminalelor, care ar trebui inițializat înainte ca un canal să fie activat. Adresa primei locații de memorie care urmează să fie accesată este încărcată în registrul de adrese DMA. Ordinea inferioară de 14 biți a valorii încărcate în registrul de numărare a terminalelor indică numărul de cicluri DMA minus unul înainte de activarea ieșirii numărării terminalului. Tipul de operație pentru un canal este indicat de cei mai semnificativi doi biți ai registrului de numărare a terminalelor.

8257 Diagrama pinilor

Avantajele și dezavantajele controlerului DMA

Avantajele și dezavantajele controlerului DMA includ următoarele.

Avantaje

- DMA accelerează operațiunile de memorie prin ocolirea implicării procesorului.

- Supraîncărcarea de lucru pe CPU scade.

- Pentru fiecare transfer, sunt necesare doar câteva numere de cicluri de ceas

Dezavantaje

- Problema coerenței cache poate fi văzută atunci când DMA este utilizat pentru transferul de date.

- Crește prețul sistemului.

DMA ( Acces direct la memorie ) controlerul este utilizat în plăci grafice, plăci de rețea, plăci de sunet etc ... DMA este, de asemenea, utilizat pentru transferul intra-chip în procesoare multi-core. Operând într-unul dintre cele trei moduri, DMA poate reduce considerabil încărcarea procesorului. În care dintre modurile DMA ați lucrat? Care dintre modurile pe care le considerați este mai eficient?