buclă blocată în fază este unul dintre blocurile de bază ale sistemelor electronice moderne. Este utilizat în general în multimedia, comunicare și în multe alte aplicații. Există două tipuri diferite de PLL - liniare și neliniare. Neliniarul este dificil și complicat de proiectat în lumea reală, dar teoria controlului liniar este bine modelată în PLL-uri analogice. PLL a demonstrat că un model liniar este suficient pentru majoritatea aplicațiilor electronice.

Ce este o buclă blocată de fază?

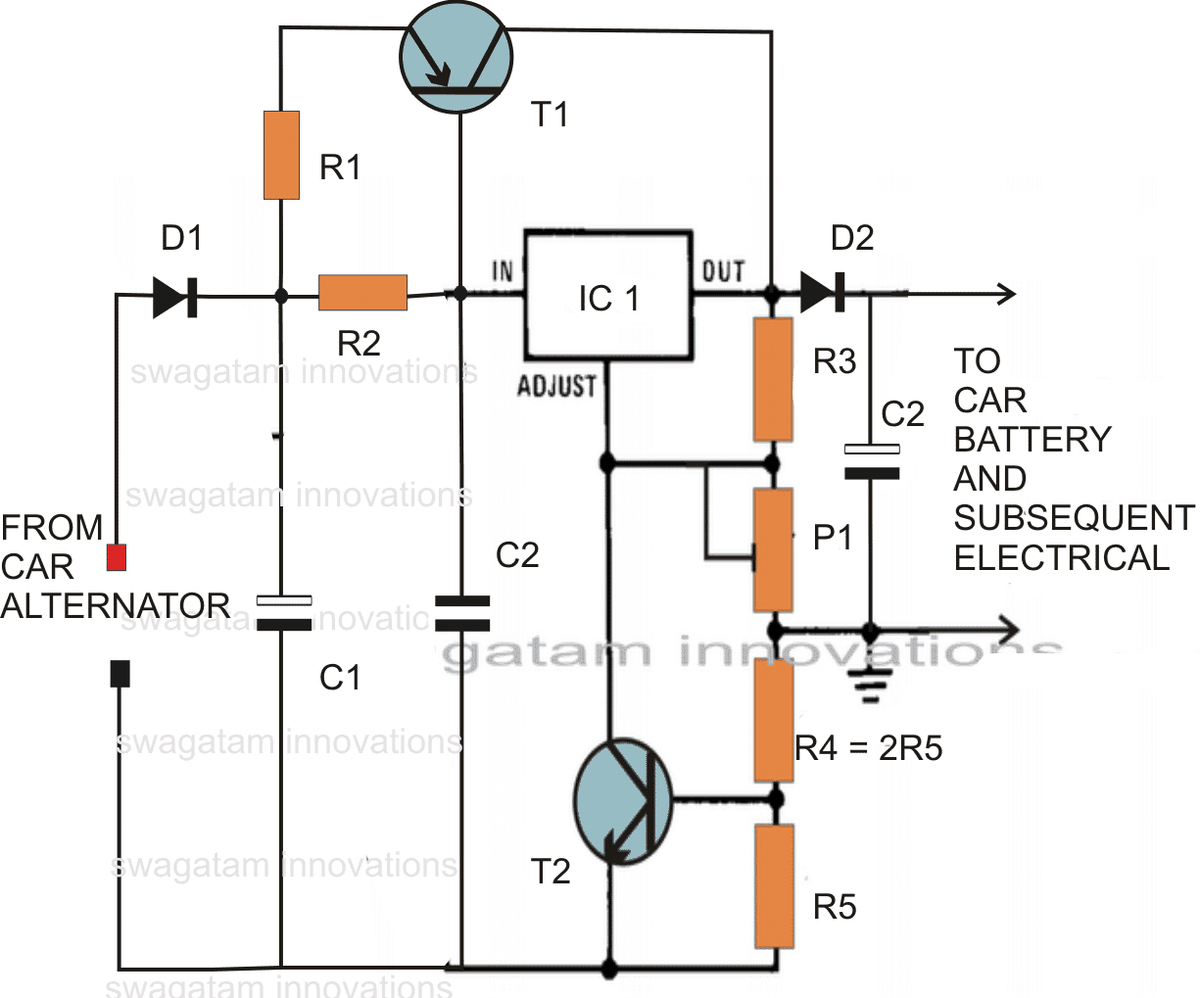

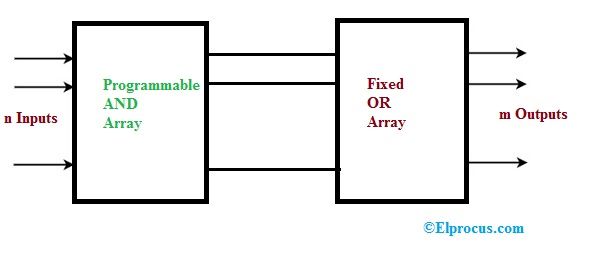

O buclă blocată în fază constă dintr-un detector de fază și un oscilator controlat de tensiune. Ieșirea detectorului de fază este intrarea oscilatorului controlat de tensiune (VCO), iar ieșirea VCO este conectată la una dintre intrările unui detector de fază, care este prezentată mai jos în diagrama bloc de bază. Când aceste două dispozitive se alimentează reciproc, se formează bucla.

DIAGRAMA DE BAZĂ A BAZEI BLOCATE DE FAZĂ

Diagrama bloc și principiul de lucru al PLL

Bucla blocată de fază constă dintr-un detector de fază, a oscilator controlat de tensiune și, între ele, este fixat un filtru trece jos. Semnalul de intrare „Vi” cu o frecvență de intrare „Fi” este acordat de un detector de fază. Practic detectorul de fază este un comparator care compară frecvența de intrare fi prin frecvența de feedback fo. Ieșirea detectorului de fază este (fi + fo), care este o tensiune continuă. Detectorul de fază, adică tensiunea de curent continuu este introdus în filtrul de trecere joasă (LPF), elimină zgomotul de înaltă frecvență și produce un nivel constant de CC, adică Fi-Fo. Vf este, de asemenea, o caracteristică dinamică a PLL.

Diagrama bloc PLL

Ieșirea filtrului trece jos, adică nivelul DC este transmis la VCO. Semnalul de intrare este direct proporțional cu frecvența de ieșire a VCO (fo). Frecvențele de intrare și ieșire sunt comparate și ajustate prin bucla de feedback până când frecvența de ieșire este egală cu frecvența de intrare. Prin urmare, PLL funcționează ca rularea gratuită, captura și blocarea fazelor.

Atunci când nu există tensiune de intrare aplicată, atunci se spune că este o etapă de funcționare liberă. De îndată ce frecvența de intrare aplicată VOC se modifică și produce o frecvență de ieșire pentru comparație, aceasta se numește etapă de captare. Figura de mai jos prezintă schema bloc a PLL.

Detector de buclă blocat de fază

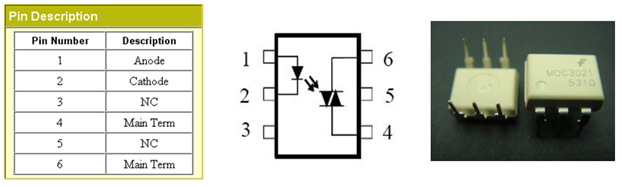

Detectorul de buclă blocat în fază compară frecvența de intrare și frecvența de ieșire a VCO pentru a produce o tensiune DC care este direct proporțională cu distincția de fază a celor două frecvențe. Semnalele analogice și digitale sunt utilizate în bucla blocată în fază. Majoritatea PLL monolitice circuite integrate utilizați un detector de fază analogic și majoritatea detectoarelor de fază sunt de tip digital. Un circuit de amestec dublu echilibrat este utilizat în mod obișnuit în detectoarele de fază analogice. Unele detectoare de fază comune sunt prezentate mai jos:

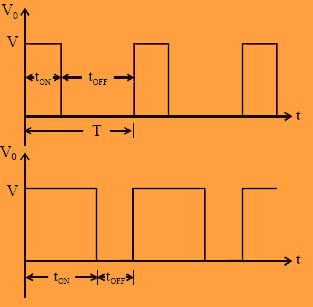

Detector de fază SAU exclusiv

Un detector de fază SAU exclusiv este de tip CMOS IC 4070. Frecvențele de intrare și ieșire sunt aplicate detectorului de fază EX OR. Pentru a obține o ieșire ridicată, cel puțin o intrare ar trebui să fie scăzută, iar celelalte condiții de ieșire să fie reduse, ceea ce se arată în tabelul de mai jos. Să luăm în considerare forma de undă, frecvențele de intrare și ieșire, adică fi și fo au o diferență de fază de 0 grade. Apoi, tensiunea de ieșire DC a comparatorului va fi o funcție a diferenței de fază dintre cele două intrări.

| fi | fo | Vdc |

scăzut | scăzut | scăzut |

scăzut | înalt | înalt |

înalt | Scăzut | înalt |

Înalt | Înalt | scăzut |

Funcțiile diferenței de fază dintre fi și fo sunt așa cum se arată în graficul tensiunii de ieșire DC. Dacă detectorul de fază este de 180 de grade, atunci tensiunea de ieșire este maximă. Dacă atât frecvențele de intrare cât și cele de ieșire sunt unde pătrate, se utilizează acest tip de detectoare de fază.

Detector de fază SAU exclusiv

Detector de fază Edge Trigger

Un detector de fază de declanșare a muchiei este utilizat atunci când frecvențele de intrare și ieșire sunt în formă de undă a impulsului, care este mai mică de 50% ciclu de funcționare. Flip flop-ul R-S este utilizat pentru detectoarele de fază, care este prezentat în figura de mai jos. Pentru a de la R-S șlap , cele două porți NOR sunt cuplate încrucișat. Ieșirea detectorului de fază își poate schimba starea logică prin declanșarea flip-flop-ului R-S. Marginea pozitivă a frecvențelor de intrare și ieșire poate modifica ieșirea detectorului de fază.

Detector de fază Edge Trigger

Detector de faze monolitice

Un detector de fază monolitic este de tip CMOS, adică IC 4044. Este foarte compensat din sensibilitatea armonică și problemele legate de ciclul de funcționare sunt abandonate deoarece circuitul poate răspunde doar la tranziția semnalului de intrare. În aplicațiile critice, este cel mai febril detector de fază. Variațiile independente ale amplitudinii sunt libere de eroarea de fază, tensiunea de eroare de ieșire și ciclul de funcționare al formelor de undă de intrare.

Aplicații buclă blocată în fază

- Rețele de demodulare FM pentru operațiuni FM

- Este folosit în comenzi ale vitezei motorului și filtre de urmărire.

- Este folosit în decodele de schimbare a frecvenței pentru frecvențele purtătoare de demodulare.

- Este folosit în timp pentru convertoarele digitale.

- Se folosește pentru reducerea jitterului, suprimarea înclinării, recuperarea ceasului.

Totul se referă la principiul de funcționare și funcționare al buclei blocate în fază și aplicațiile sale. Sperăm că informațiile furnizate în articol vă vor fi de ajutor pentru a afla ceva despre proiect și a-l înțelege. Mai mult, dacă aveți întrebări cu privire la acest articol și mai departe proiecte electrice și electronice puteți comenta în secțiunea de mai jos. Iată o întrebare pentru dvs., care este cel mai bun mod de a simula PLL pentru stabilitate?

Credite foto:

- Diagrama bloc a PLL astăzi în circuit

- Detector de fază SAU exclusiv sanfoundry

- Detector de fază Edge Trigger ÎNVĂȚARE-ELECTRONICĂ