Setul de instrucțiuni sau arhitectura setului de instrucțiuni este structura computerului care furnizează comenzi către computer pentru a ghida computerul pentru procesarea manipulării datelor. Setul de instrucțiuni constă din instrucțiuni, moduri de adresare, tipuri de date native, registre, întreruperi, gestionarea excepțiilor și arhitectura memoriei. Setul de instrucțiuni poate fi imitat în software folosind un interpret sau încorporat în hardware-ul procesorului. Arhitectura setului de instrucțiuni poate fi considerată ca o graniță între software și hardware. Clasificarea microcontrolerelor iar microprocesoarele pot fi realizate pe baza arhitecturii setului de instrucțiuni RISC și CISC.

Set de instrucțiuni de procesor

Setul de instrucțiuni specifică funcționalitatea procesorului, inclusiv operațiunile acceptate de procesor, mecanismele de stocare ale procesorului și modul de compilare a programelor către procesor.

Ce este RISC și CISC?

RISC și CISC poate fi extins după cum urmează:

RISC reprezintă calculatorul setului de instrucțiuni reduse și

CISC reprezintă computerul complex de instrucțiuni.

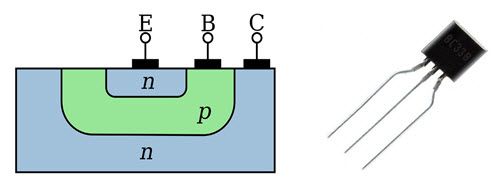

Arhitectură RISC (Reduced Instruction Set Computer)

RISC Architecture

arhitectura microcontrolerului care utilizează un set de instrucțiuni mic și extrem de optimizat este denumit Computer Reduced Set Set sau este numit pur și simplu RISC. Se mai numește și arhitectură LOAD / STORE.

La sfârșitul anilor 1970 și începutul anilor 1980, proiectele RISC au fost dezvoltate în principal din Stanford, UC-Berkley și IBM. Echipa de cercetare John Coke de la IBM a dezvoltat RISC prin reducerea numărului de instrucțiuni necesare procesării calculelor mai rapid decât CISC. Arhitectura RISC este mai rapidă și cipurile necesare pentru fabricarea arhitecturii RISC sunt, de asemenea, mai puțin costisitoare comparativ cu arhitectura CISC.

Caracteristici tipice ale arhitecturii RISC

- Tehnica de canalizare a RISC, execută mai multe părți sau etape de instrucțiuni simultan, astfel încât fiecare instrucțiune de pe CPU să fie optimizată. Prin urmare, procesoarele RISC au Ceas pe Instrucțiune de un ciclu, iar acest lucru se numește Execuție cu un singur ciclu.

- Optimizează utilizarea registrului cu un număr mai mare de registre în RISC și un număr mai mare de interacțiuni în memorie pot fi prevenite.

- Moduri de adresare simple, chiar și adresări complexe se pot face folosind aritmetica ȘI / SAU operațiuni logice .

- Simplifică proiectarea compilatorului utilizând registre identice de uz general care permit utilizarea oricărui registru în orice context.

- Pentru utilizarea eficientă a registrelor și optimizarea utilizărilor de conducte, este necesar un set de instrucțiuni redus.

- Numărul de biți utilizați pentru opcode este redus.

- În general, există 32 sau mai multe registre în RISC.

Avantajele arhitecturii procesorului RISC

- Datorită setului mic de instrucțiuni ale RISC, compilatoarele de limbaj la nivel înalt pot produce coduri mai eficiente.

- RISC permite libertatea de utilizare a spațiului activat microprocesoare datorită simplității sale.

- În loc să folosească Stack, mulți procesoare RISC folosesc registrele pentru transmiterea argumentelor și păstrarea variabilelor locale.

- Funcțiile RISC utilizează doar câțiva parametri, iar procesoarele RISC nu pot utiliza instrucțiunile de apel și, prin urmare, utilizează instrucțiuni cu lungime fixă, ușor de realizat.

- Viteza operației poate fi maximizată și timpul de execuție poate fi minimizat.

- Este nevoie de un număr foarte mic de formate de instrucțiuni (mai puțin de patru), un număr de instrucțiuni (aproximativ 150) și câteva moduri de adresare (mai puțin de patru).

Dezavantaje ale arhitecturii procesorului RISC

- Odată cu creșterea în lungime a instrucțiunilor, complexitatea crește pentru a fi executate de procesoarele RISC datorită ciclului său de caractere pe instrucțiune.

- Performanța procesorelor RISC depinde în mare parte de compilator sau programator, deoarece cunoștințele compilatorului joacă un rol major în timp ce convertesc codul CISC într-un cod RISC, prin urmare, calitatea codului generat depinde de compilator.

- În timp ce reprogramarea codului CISC la un cod RISC, denumit ca o extindere a codului, va crește dimensiunea. Și, calitatea acestei extinderi de cod va depinde din nou de compilator și, de asemenea, de setul de instrucțiuni al mașinii.

- Cache-ul de primul nivel al procesoarelor RISC este, de asemenea, un dezavantaj al RISC, în care aceste procesoare au cache-uri de memorie mari pe cipul în sine. Pentru hrănirea instrucțiunilor, acestea necesită foarte mult sisteme de memorie rapide .

Arhitectură CISC (Complex Instruction Set Computer)

Scopul principal al arhitecturii procesorului CISC este de a finaliza sarcina utilizând un număr mai mic de linii de asamblare. În acest scop, procesorul este construit pentru a executa o serie de operații. Instrucțiunea complexă este denumită și MULT, care funcționează bănci de memorie unui computer direct fără a face compilatorul să efectueze funcții de stocare și încărcare.

Arhitectura CISC

Caracteristicile arhitecturii CISC

- Pentru a simplifica arhitectura computerului, CISC acceptă microprogramarea.

- CISC are mai multe instrucțiuni predefinite, ceea ce face ca limbile de nivel înalt să fie ușor de proiectat și implementat.

- CISC constă într-un număr mai mic de registre și un număr mai mare de moduri de adresare, în general de la 5 la 20.

- Procesorul CISC necesită timp de ciclu diferit pentru executarea instrucțiunilor - cicluri cu mai multe ceasuri.

- Datorită setului complex de instrucțiuni al CISC, tehnica de conducte este foarte dificilă.

- CISC constă într-un număr mai mare de instrucțiuni, în general de la 100 la 250.

- Instrucțiuni speciale sunt folosite foarte rar.

- Operanzii din memorie sunt manipulați prin instrucțiuni.

Avantajele arhitecturii CISC

- Fiecare instrucțiune de limbaj mașină este grupată într-o instrucțiune de microcod și executată corespunzător și apoi este stocată încorporată în memoria procesorului principal, denumită implementare de microcod.

- Deoarece memoria microcodului este mai rapidă decât memoria principală, setul de instrucțiuni pentru microcoduri poate fi implementat fără reducerea considerabilă a vitezei față de implementarea prin cablu.

- Întregul set de instrucțiuni nou poate fi gestionat prin modificarea designului microprogramului.

- CISC, numărul instrucțiunilor necesare pentru implementarea unui program poate fi redus prin construirea unor seturi de instrucțiuni bogate și poate fi, de asemenea, utilizat pentru a utiliza memoria principală lentă mai eficient.

- Datorită supersetului de instrucțiuni care constă din toate instrucțiunile anterioare, acest lucru ușurează codarea micro.

Dezavantaje ale CISC

- Durata ceasului luată de instrucțiuni diferite va fi diferită - datorită acestui fapt - performanța mașinii încetinește.

- Complexitatea setului de instrucțiuni și hardware-ul cipului crește pe măsură ce fiecare nouă versiune a procesorului constă dintr-un subset de generații anterioare.

- Doar 20% din instrucțiunile existente sunt utilizate într-un eveniment tipic de programare, chiar dacă există multe instrucțiuni specializate care nici măcar nu sunt utilizate frecvent.

- Codurile condiționale sunt setate de instrucțiunile CISC ca efect secundar al fiecărei instrucțiuni care necesită timp pentru această setare - și, pe măsură ce instrucțiunea ulterioară modifică biții de cod de condiție - astfel, compilatorul trebuie să examineze biții de cod de condiție înainte ca acest lucru să se întâmple.

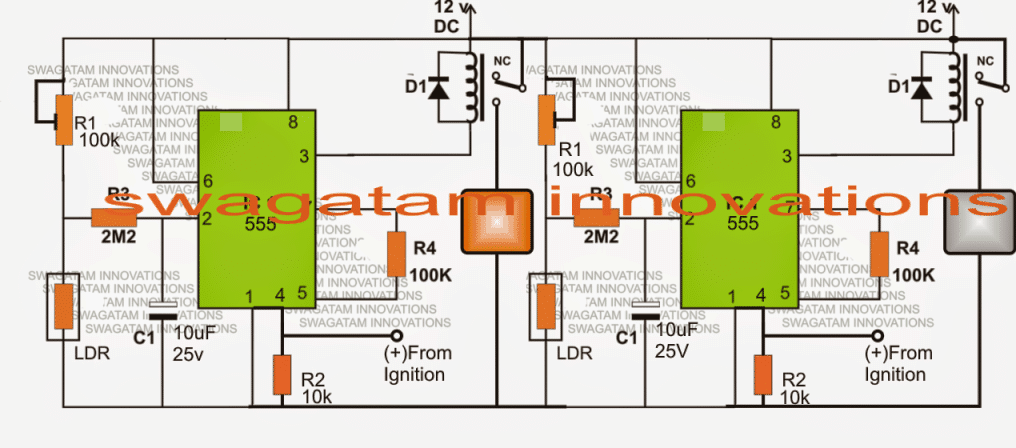

RISC vs. CISC

- Ciclurile de pierdere pot fi prevenite de programator prin eliminarea codului inutil din RISC, dar, în timp ce se utilizează codul CISC, se duc la cicluri de pierdere din cauza ineficienței CISC.

- În RISC, fiecare instrucțiune este destinată să efectueze o sarcină mică, astfel încât, pentru a efectua o sarcină complexă, mai multe instrucțiuni mici să fie utilizate împreună, în timp ce doar câteva instrucțiuni sunt necesare pentru a face aceeași sarcină folosind CISC - deoarece este capabil să efectueze sarcini complexe deoarece instrucțiunile sunt similare cu un cod în limbă mare.

- CISC este de obicei utilizat pentru computere, în timp ce RISC este utilizat pentru telefoane inteligente, tablete și alte dispozitive electronice.

Următoarea figură arată mai multe diferențe între RISC și CISC

RISC vs. CISC

Astfel, acest articol discută despre caracteristicile arhitecturilor RISC și CISC ale avantajelor arhitecturii procesorilor RISC și CISC și dezavantajele RISC și CISC, precum și despre diferențele dintre arhitecturile RISC și CISC cu o scurtă idee. Pentru mai multe informații cu privire la arhitecturile RISC și CISC, vă rugăm să postați întrebările dvs. comentând mai jos.

Credite foto:

- Set de instrucțiuni de procesor de arstechnica

- RISC Architecture de lsi-concurs

- RISC vs. CISC de csarassignment